在移动通信网络飞速发展的今天,射频(RF)集成电路作为连接数字世界与无线电磁波的关键桥梁,其性能直接决定了通信设备的速度、效率与可靠性。混合信号RF集成电路,集成了模拟RF前端与数字基带处理,是现代通信芯片的核心。随着通信标准向5G Advanced及6G演进,对带宽、线性度、噪声和功耗等指标提出了近乎严苛的要求,改进其RF性能已成为行业技术攻关的焦点。

一、 核心挑战:性能瓶颈与干扰

改进混合信号RF电路性能,首先需直面其固有挑战:

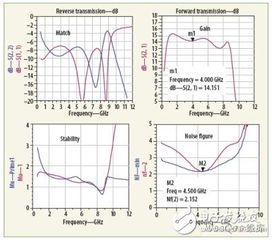

- 噪声与灵敏度:在接收路径,低噪声放大器(LNA)的噪声系数(NF)直接限制了系统的接收灵敏度。模拟电路中的闪烁噪声(1/f噪声)和热噪声在深亚微米工艺下更为显著。

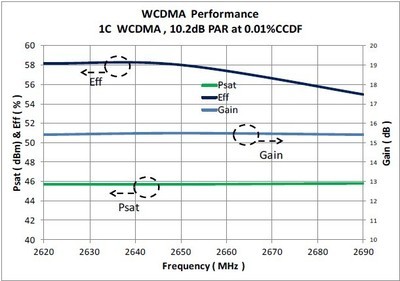

- 线性度与动态范围:发射功率放大器(PA)的线性度(如IP3)必须足够高,以处理高峰均比(PAPR)的现代调制信号(如OFDM),避免频谱再生和邻道干扰。系统需在强干扰信号下保持对小信号的接收能力,即拥有高动态范围。

- 功耗与效率:尤其是在基站和移动终端中,PA的效率(如功率附加效率PAE)至关重要,直接影响设备续航和散热设计。

- 集成度与隔离度:数字电路(如高速时钟和数据转换器)与敏感的模拟RF电路集成在同一芯片上,数字开关噪声(地弹、电源噪声)极易通过衬底耦合和电源线耦合干扰RF信号,导致性能劣化。

- 工艺限制:先进CMOS工艺虽提升了数字电路的密度与速度,但晶体管的截止频率(fT)和击穿电压等模拟特性并未同步线性提升,对设计高功率、高频RF电路构成约束。

二、 关键技术改进方向

针对上述挑战,业界从架构、电路设计和工艺协同等多维度进行创新:

1. 先进的系统架构

- 数字辅助射频技术:利用数字校准和预失真(DPD)技术,在数字域补偿PA的非线性与记忆效应,显著提升线性度和效率。同样,数字校准可用于校正数据转换器(ADC/DAC)的失配和频率响应。

- 软件定义无线电(SDR)与可重构架构:通过软件配置射频前端参数,使单一硬件平台支持多频段、多模式,并通过算法优化实时调整性能权衡。

2. 电路级创新设计

- 低噪声与高线性度电路拓扑:探索如噪声抵消技术、电流复用技术、互补衍生结构等,在功耗不变的前提下优化NF和IP3。对于PA,采用Doherty、包络跟踪(ET)等高效架构已成为主流。

- 高性能数据转换器:设计高精度、高采样率的RF-DAC和RF-ADC,推动射频信号链进一步“数字化”,减少对复杂模拟滤波器的依赖。采用时间交织、噪声整形等技术提升性能。

- 电源与偏置优化:采用低压差线性稳压器(LDO)、开关电容稳压器或包络调制电源,为RF关键模块提供“清洁”、高效的供电,抑制电源噪声。

3. 版图、封装与隔离技术

- 版图隔离策略:采用深N阱、保护环、隔离槽(如SOI工艺中的氧化埋层)等技术,增加数字与模拟/RF电路之间的衬底隔离。关键RF走线使用顶层厚金属,并注重屏蔽和阻抗匹配。

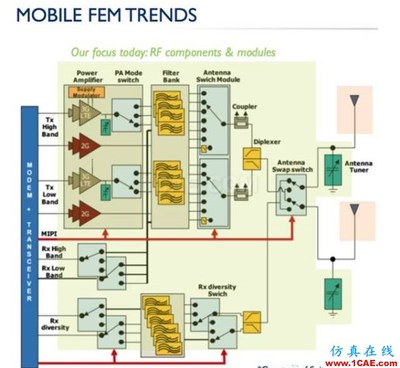

- 先进封装集成:采用扇出型晶圆级封装(Fan-Out WLP)、系统级封装(SiP)或硅桥技术,将优化的RF芯片(可能采用GaAs、SiGe等特殊工艺)与数字核心芯片异构集成,实现性能与成本的最佳平衡,同时减少片内干扰。

4. 工艺与建模协同

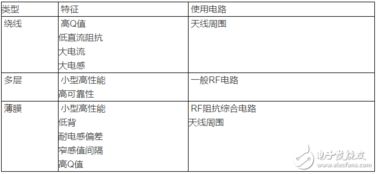

- FD-SOI与RF CMOS工艺:全耗尽型绝缘体上硅(FD-SOI)工艺因其出色的背面偏置控制能力和更低的寄生电容,在低功耗、高性能RF设计中展现出优势。RF CMOS工艺库则提供经过充分表征的射频无源器件(如高品质因数Q的电感、变容二极管)和精确的射频模型。

- 协同设计与仿真:建立包含封装寄生参数、版图电磁效应(EM)的系统级仿真环境,实现从系统架构到晶体管级的全链路协同优化,提前预知并解决潜在的信号完整性和干扰问题。

三、 与展望

改进混合信号RF集成电路的RF性能是一项系统工程,它不再仅仅是模拟电路设计师的职责,而是需要系统架构师、数字算法工程师、版图设计师和工艺工程师的深度协同。随着人工智能/机器学习技术的引入,有望实现RF性能的自主在线优化与故障预测。面向太赫兹频段的6G通信,基于III-V族化合物半导体与硅基CMOS的异质集成技术,将成为突破性能极限的关键路径。通过持续的技术融合与创新,混合信号RF IC将持续为移动通信网络注入更强大、更智能的无线连接能力。